One of the FIB services NanoPhysics has to offer is circuit edit, which is a powerful technique to enhance the development of a new integrated circuit. When failures arise after first time tests FIB Circuit edit can modify the chip rapidly and debug the chip without waiting preparing a new mask.

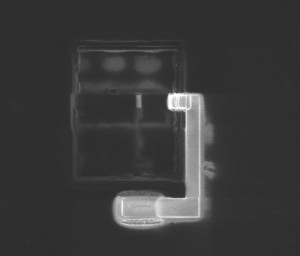

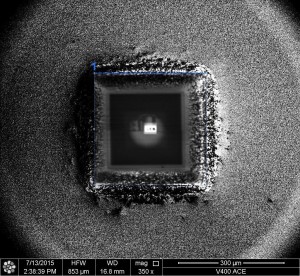

FIB chip modification can be done from frontside so only decapsulation is required. But we also offer backside circuit modification. This can be performed on all kind of packages like WLCSP, QFN, flip-chip, SOT and even BGA's in some cases. For this backside circuit edit we need to thin down the bulk silicon of the die. After that we can trench a big hole in the silicon to get access to the active area of the chip (see image below on this page).

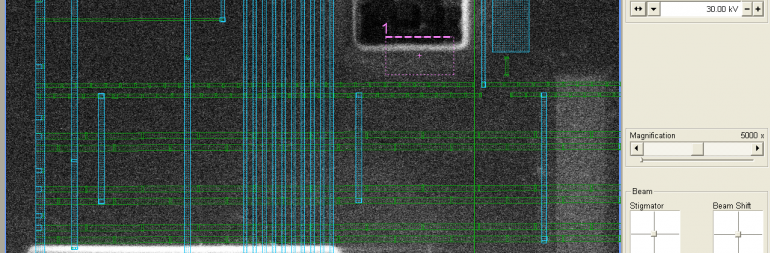

By applying FIB milling unwanted connections on the chip can be removed and new metal tracks are deposited. FIB milling uses a beam of finely focused Ga+ ions that are accelerated to 30 KeV and scans the surface of the sample. So the FIB can mill away materials starting from the surface into a chip for instance. When gases are used during milling, metal tracks or insulated layers can be deposit. This way FIB circuit edit is a fast microsurgery tool for first silicon debugging. Our circuit edit include both Aluminium and copper based chips for front as well as backside modification.

NanoPhysics B.V. uses a FEI V600CE (V600 Circuit Edit) and a FEI V400ACE (V400 Circuit Edit) with a navigation driven stage for precise FIB milling within nm resolution. NanoPhysics B.V. guarantees a fast turnaround time for your circuit edit and offer competitive pricing. Together with our years of experience makes NanoPhysics your choice for circuit editing.

Feel free to contact us in case you like to know more about our FIB circuit edit service.

More Services: SEM-EDX, Chip Deprocessing, FIB cross sectioning, Competitor Analysis, FIB Circuit Edit, Failure Analysis, Patent Infringement analysis